16-to-1 multiplexer (16X1 MUX) Verilog

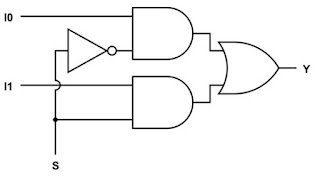

Bottom-UP Hierarchical Structure Structure modeling of 2-to-1 MUX 4-to-1 MUX using two 2-to-1 MUX 8-to-1 MUX using two 4-to-1 MUX 16-to-1 MUX usng two 8-to-1 MUX 1. Structural Modeling of 2-to-1 MUX Design Code _________________________________________________________________________________ module MUX_2X1(input I0, I1, S, output Y); wire sbar, w1, w2, Y; not G1 (sbar, S); and G2 (w1, I0, sbar); and G3 (w2, I1, S); or G4 (Y, w1, w2); endmodule _________________________________________________________________________________ Test Bench _________________________________________________________________________________ module MUX_test; reg [2:0] x; wire z; MUX_2X1 M1 (x[0], x[1], x[2], z); initial begin $display("\t\t Time\tSelect A B \t Z"); $monit...