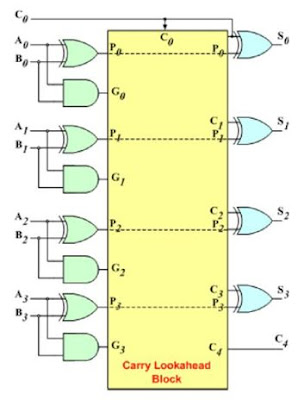

Carry Lookahead 4-bit Adder Verilog

Logic Diagram for Sums

Logic Diagram for Carries

There are two important variables in Carry lookahead Adder

- Carry Generate Component Gi: It state that output carry Ci+1 is generated irrespective input carry Ci. This state occurs when both inputs Ai and Bi are 1.

- so Gi = Ai.Bi

- Carry Propagate Component Pi: It state that input carry Ci is propagated to output carry Ci+1. In other words, in this state the output carry Ci+1 is equal to input carry Ci. This state occurs when either of input is 1, other is 0. (or One input is compliment of other input).

- So Pi = Ai^Bi

- Overall equation for output carry Ci+1 = Gi + Pi.Ci (in other words, Cout = A0.B0 + (A0^B0).Cin)

- Sum = (Ai^Bi)^Ci = Pi^Ci

_________________________________________________________________________________ module Carry_Lookahead_Adder(a,b,cin,sum,cout);

input[3:0] a,b; input cin;

output [3:0] sum; output cout;

wire p0,p1,p2,p3,g0,g1,g2,g3,c1,c2,c3;

assign p0=(a[0]^b[0]), p1=(a[1]^b[1]),

p2=(a[2]^b[2]), p3=(a[3]^b[3]);

assign g0=(a[0]&b[0]), g1=(a[1]&b[1]),

g2=(a[2]&b[2]), g3=(a[3]&b[3]);

assign c1=g0|(p0&cin),

c2=g1|(p1&g0)|(p1&p0&cin),

c3=g2|(p2&g1)|(p2&p1&g0)|(p2&p1&p0&cin),

cout=g3|(p3&g2)|(p3&p2&g1)|(p3&p2&p1&g0)|(p3&p2&p1&p0&cin);

assign sum[0]=p0^cin,

sum[1]=p1^c1,

sum[2]=p2^c2,

sum[3]=p3^c3;

endmodule

_________________________________________________________________________________

Test Bench

________________________________________________________________________________

// Code your testbench here

// or browse Examples

module Adder_test;

reg [3:0] A, B;

reg C0;

wire [3:0] S;

wire C4;

integer i, f1, f2;

bit Flag; // Flag = 1 when there is error in o/p

Carry_Lookahead_Adder ADD1 (A, B, C0, S, C4);

initial

begin

f1 = 0;

f2 = 0;

Flag = 1'b0;

$display("A(hexa) B(hexa) Cin(Bit) \t S(hexa) Cout(bit) \t Flag");

for (i=0; i<16; i=i+1)

begin

A = i;

B = i+1;

C0 = i%2;

#5 f1 = ((2*i)+1+(i%2));

f2 = ({C4, S}); // S+(C4*16);

if (f1 != f2)

Flag = 1;

$display("%h \t %h \t %b \t\t %h \t %b \t \t %d", A[3:0], B[3:0], C0, S[3:0], C4, Flag);

end

#5 $finish;

end

endmodule

_________________________________________________________________________________

Output

A(hexa) B(hexa) Cin(Bit) S(hexa) Cout(bit) Flag

0 1 0 1 0 0

1 2 1 4 0 0

2 3 0 5 0 0

3 4 1 8 0 0

4 5 0 9 0 0

5 6 1 c 0 0

6 7 0 d 0 0

7 8 1 0 1 0

8 9 0 1 1 0

9 a 1 4 1 0

a b 0 5 1 0

b c 1 8 1 0

c d 0 9 1 0

d e 1 c 1 0

e f 0 d 1 0

f 0 1 0 1 1 it is basically an overflow error

0 1 0 1 0 0

1 2 1 4 0 0

2 3 0 5 0 0

3 4 1 8 0 0

4 5 0 9 0 0

5 6 1 c 0 0

6 7 0 d 0 0

7 8 1 0 1 0

8 9 0 1 1 0

9 a 1 4 1 0

a b 0 5 1 0

b c 1 8 1 0

c d 0 9 1 0

d e 1 c 1 0

e f 0 d 1 0

f 0 1 0 1 1 it is basically an overflow error

_________________________________________________________________________________

Code

module Carry_Lookahead_Adder(a,b,cin,sum,cout);

input[3:0] a,b; input cin;

output [3:0] sum; output cout;

wire p0,p1,p2,p3,g0,g1,g2,g3,c1,c2,c3;

assign p0=(a[0]^b[0]), p1=(a[1]^b[1]),

p2=(a[2]^b[2]), p3=(a[3]^b[3]);

assign g0=(a[0]&b[0]), g1=(a[1]&b[1]),

g2=(a[2]&b[2]), g3=(a[3]&b[3]);

assign c1=g0|(p0&cin),

c2=g1|(p1&g0)|(p1&p0&cin),

c3=g2|(p2&g1)|(p2&p1&g0)|(p1&p1&p0&cin),

cout=g3|(p3&g2)|(p3&p2&g1)|(p3&p2&p1&g0)|(p3&p2&p1&p0&cin);

assign sum[0]=p0^cin,

sum[1]=p1^c1,

sum[2]=p2^c2,

sum[3]=p3^c3;

endmodule

Output

_______________________________________________________________________________

A(hexa) B(hexa) Cin(Bit) S(hexa) Cout(bit) Flag

0 1 0 1 0 0

1 2 1 c 0 1

2 3 0 5 0 1

3 4 1 8 0 1

4 5 0 9 0 1

5 6 1 c 0 1

6 7 0 d 0 1

7 8 1 0 1 1

8 9 0 1 1 1

9 a 1 c 1 1

a b 0 5 1 1

b c 1 8 1 1

c d 0 9 1 1

d e 1 c 1 1

e f 0 d 1 1

f 0 1 0 1 1

__________________________________________________________________________________

How to play baccarat - WORRIione

ReplyDeleteThe most commonly played 바카라 사이트 card game 인카지노 is the 제왕카지노 Whist/Baccarat game where players bet on which team has the most points. Baccarat. In the game, the team's