N-bit Adder Verilog

N-bit Adder using generate

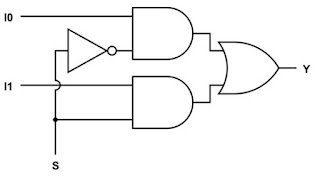

Lets examine the full adder

Lets examine the full adder

module Full_adder(output S, Cout, input A, B, Cin);

wire w1, w2, w3;

xor G1 (w1, A, B);

xor G2 (S, w1, Cin);

and G3 (w2, A, B);

and G4 (w3, w1, Cin);

or G5 (Cout, w2, w3);

endmodule

N-bits Adder requires

Two N-bits Input variables (A, B)

1-bit Cin

One N-bits Output variable (S)

1-bit Cout

N-Full Adders

and internal mapping

____________________________________________________________________________

//Design Code

module Nbit_Adder(S, Cout, A, B, Cin);

parameter N = 8;

input [N-1:0] A, B;

input Cin;

output [N-1:0] S;

output Cout;

wire [N:0] C;

assign C[0] = Cin;

assign Cout = C[N];

genvar i;

generate for (i=0; i<N ; i=i+1)

begin

wire w1, w2, w3;

xor G1 (w1, A[i], B[i]);

xor G2 (S[i], w1, C[i]);

and G3 (w2, A[i], B[i]);

and G4 (w3, w1, C[i]);

or G5 (C[i+1], w2, w3);

end

endgenerate

endmodule

____________________________________________________________________________

//Test Bench

module Adder_test;

reg [7:0] A, B;

reg C0;

wire [7:0] S;

wire C4;

Nbit_Adder ADD1 (S, C4, A, B, C0);

initial

begin

$display("A(hexa) B(hexa) Cin(Bit) \t S(hexa) Cout(bit)");

$monitor("%h \t %h \t %b \t\t %h \t %b", A[7:0], B[7:0], C0, S[7:0], C4);

A = 8'h00; B = 8'h00; C0 = 1'b0;

#5 A = 8'h01; B = 8'h01; C0 = 1'b1;

#5 A = 8'h01; B = 8'h09; C0 = 1'b0;

#5 A = 8'h0E; B = 8'h00; C0 = 1'b1;

#5 A = 8'hFF; B = 8'h01; C0 = 0'b1;

#5 $finish;

end

endmodule

____________________________________________________________

Output

A(hexa) B(hexa) Cin(Bit) S(hexa) Cout(bit)

00 00 0 00 0

01 01 1 03 0

01 09 0 0a 0

0e 00 1 0f 0

ff 01 0 00 1

00 00 0 00 0

01 01 1 03 0

01 09 0 0a 0

0e 00 1 0f 0

ff 01 0 00 1

_______________________________________________________________

Comments

Post a Comment