8 bit Adder Verilog

Eight bit Adder

By cascading of two - 4-bit Adders

Design Code

_________________________________________________________________________________

module Adder_8bit(input [7:0] A, B, input Cin, output [7:0] S, output Cout);

wire Cout1;

Adder_4bit ADD1 (A[3:0], B[3:0], Cin, S[3:0], Cout1);

Adder_4bit ADD2 (A[7:4], B[7:4], Cout1, S[7:4], Cout);

endmodule

module Adder_4bit(input [3:0] A, B, input C0, output [3:0] S, output C4);

wire C1, C2, C3;

Full_adder FA0 (S[0], C1, A[0], B[0], C0);

Full_adder FA1 (S[1], C2, A[1], B[1], C1);

Full_adder FA2 (S[2], C3, A[2], B[2], C2);

Full_adder FA3 (S[3], C4, A[3], B[3], C3);

endmodule

module Full_adder(output S, C1, input A, B, C0);

wire w1, w2, w3;

Half_Adder HA1 (w1, w2, A, B);

Half_Adder HA2 (S, w3, w1, C0);

or_function G1 (C1, w2, w3);

endmodule

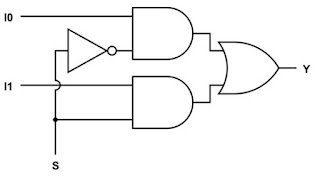

module Half_Adder(output S, C, input A, B);

xor G1 (S, A, B);

and G2 (C, A, B);

endmodule

module or_function(output f, input a, b);

or G1 (f, a, b);

endmodule

_______________________________________________________________________________

Test Bench

________________________________________________________________________________

module Adder_test;

reg [7:0] A, B;

reg C0;

wire [7:0] S;

wire C4;

Adder_8bit ADD1 (A, B, C0, S, C4);

initial

begin

$display("A(hexa) B(hexa) Cin(Bit) \t S(hexa) Cout(bit)");

$monitor("%h \t %h \t %b \t\t %h \t %b", A[7:0], B[7:0], C0, S[7:0], C4);

A = 8'h00; B = 8'h00; C0 = 1'b0;

#5 A = 8'h01; B = 8'h01; C0 = 1'b1;

#5 A = 8'h01; B = 8'h09; C0 = 1'b0;

#5 A = 8'h0E; B = 8'h00; C0 = 1'b1;

#5 A = 8'hFF; B = 8'h01; C0 = 0'b1;

#5 $finish;

end

endmodule

________________________________________________________________________________

Output

___________________________________________________________

A(hexa) B(hexa) Cin(Bit) S(hexa) Cout(bit)

00 00 0 00 0

01 01 1 03 0

01 09 0 0a 0

0e 00 1 0f 0

ff 01 0 00 1

___________________________________________________________

By cascading of two - 4-bit Adders

Design Code

_________________________________________________________________________________

module Adder_8bit(input [7:0] A, B, input Cin, output [7:0] S, output Cout);

wire Cout1;

Adder_4bit ADD1 (A[3:0], B[3:0], Cin, S[3:0], Cout1);

Adder_4bit ADD2 (A[7:4], B[7:4], Cout1, S[7:4], Cout);

endmodule

module Adder_4bit(input [3:0] A, B, input C0, output [3:0] S, output C4);

wire C1, C2, C3;

Full_adder FA0 (S[0], C1, A[0], B[0], C0);

Full_adder FA1 (S[1], C2, A[1], B[1], C1);

Full_adder FA2 (S[2], C3, A[2], B[2], C2);

Full_adder FA3 (S[3], C4, A[3], B[3], C3);

endmodule

module Full_adder(output S, C1, input A, B, C0);

wire w1, w2, w3;

Half_Adder HA1 (w1, w2, A, B);

Half_Adder HA2 (S, w3, w1, C0);

or_function G1 (C1, w2, w3);

endmodule

module Half_Adder(output S, C, input A, B);

xor G1 (S, A, B);

and G2 (C, A, B);

endmodule

module or_function(output f, input a, b);

or G1 (f, a, b);

endmodule

_______________________________________________________________________________

Test Bench

________________________________________________________________________________

module Adder_test;

reg [7:0] A, B;

reg C0;

wire [7:0] S;

wire C4;

Adder_8bit ADD1 (A, B, C0, S, C4);

initial

begin

$display("A(hexa) B(hexa) Cin(Bit) \t S(hexa) Cout(bit)");

$monitor("%h \t %h \t %b \t\t %h \t %b", A[7:0], B[7:0], C0, S[7:0], C4);

A = 8'h00; B = 8'h00; C0 = 1'b0;

#5 A = 8'h01; B = 8'h01; C0 = 1'b1;

#5 A = 8'h01; B = 8'h09; C0 = 1'b0;

#5 A = 8'h0E; B = 8'h00; C0 = 1'b1;

#5 A = 8'hFF; B = 8'h01; C0 = 0'b1;

#5 $finish;

end

endmodule

________________________________________________________________________________

Output

___________________________________________________________

A(hexa) B(hexa) Cin(Bit) S(hexa) Cout(bit)

00 00 0 00 0

01 01 1 03 0

01 09 0 0a 0

0e 00 1 0f 0

ff 01 0 00 1

___________________________________________________________

Comments

Post a Comment