MUX Multiplexer Verilog

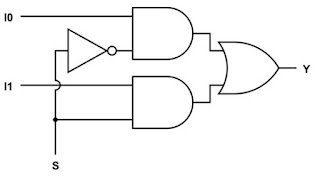

2x1 Multiplexer

For S0 = 0, Z=A

For S0 = 1, Z=B

Design Code

_____________________________________________________________________________

module MUX_2X1(A, B, S0, Z);

input A, B, S0;

output Z;

wire Z;

assign Z = S0 ? B : A; // If S0=0(false), Z=A; If S0 = 1(true), Z=B

endmodule

For S0 = 0, Z=A

For S0 = 1, Z=B

Design Code

_____________________________________________________________________________

module MUX_2X1(A, B, S0, Z);

input A, B, S0;

output Z;

wire Z;

assign Z = S0 ? B : A; // If S0=0(false), Z=A; If S0 = 1(true), Z=B

endmodule

______________________________________________________________________________

Test Bench

______________________________________________________________________________

module MUX_test;

reg [2:0] x;

wire z;

MUX_2X1 M1 (x[0], x[1], x[2], z);

initial

begin

$display("\t\t Time\tSelect A B \t Z");

$monitor($time,"\t %b \t%b %b \t %b", x[2], x[0], x[1], z);

x = 3'O0;

#5 x = 3'O1;

#5 x = 3'O2;

#5 x = 3'O3;

#5 x = 3'O4;

#5 x = 3'O5;

#5 x = 3'O6;

#5 x = 3'O7;

#5 $finish;

end

endmodule

________________________________________________________________________________

Output

_______________________________________________________________________________

Time Select A B Z

0 0 0 0 0

5 0 1 0 1

10 0 0 1 0

15 0 1 1 1

20 1 0 0 0

25 1 1 0 0

30 1 0 1 1

35 1 1 1 1

0 0 0 0 0

5 0 1 0 1

10 0 0 1 0

15 0 1 1 1

20 1 0 0 0

25 1 1 0 0

30 1 0 1 1

35 1 1 1 1

_______________________________________________________________________________

Version 2

______________________________________________________________________________

module MUX_2X1(input A, B, S0, output Z);

reg Z;

always @(A, B, S0)

begin

if (S0)

Z = A;

else

Z = B;

end

endmodule

_______________________________________________________________________________

Version 3

Since a single instruction needs to be executed under always, there is no need for begin & end

________________________________________________________________________________

module MUX_2X1(input A, B, S0, output Z);

reg Z;

always @(A, B, S0)

if (S0)

Z = B;

else

Z = A;

endmodule

________________________________________________________________________________

Version 3

_______________________________________________________________________________

primitive MUX_2X1(Z, S0, A, B);

input S0, A, B;

output Z;

table

// S0 A B : Z

0 0 ? : 0;

0 1 ? : 1;

1 ? 0 : 0;

1 ? 1 : 1;

endtable

endprimitive

______________________________________________________________________________

Test Bench

_____________________________________________________________________________

module MUX_test;

reg [2:0] x;

wire z;

MUX_2X1 M1 (z, x[2], x[0], x[1]);

initial

begin

$display("\t\t Time\tSelect A B \t Z");

$monitor($time,"\t %b \t%b %b \t %b", x[2], x[0], x[1], z);

x = 3'O0;

#5 x = 3'O1;

#5 x = 3'O2;

#5 x = 3'O3;

#5 x = 3'O4;

#5 x = 3'O5;

#5 x = 3'O6;

#5 x = 3'O7;

#5 $finish;

end

endmodule

_______________________________________________________________________________

same output

Comments

Post a Comment